# *SOKUDO*

### "Shooting for the 22nm Lithography Goal" with the

SOKUDO Lithography Breakfast Forum 2010 July 14 (L1)

## Three (3) different exposure options for 22nm:

- MAPPER Lithography on E-Beam Maskless (ML2)

- ASML on EUV Lithography & M.P. Immersion ArF

- NIKON on Multiple Patterning Immersion ArF & EUVL

## One (1) in-line coat/develop track fits all scenarios:

### Public External (L1) However, coat/develop track configuration varies significantly by photolithography technology ...

wph = wafers per hour \* Assumes E-Beam (ML2) Cluster Tool such as MAPPER Litho.

Throughput (wph) Projections

|  |           | 2011      | 2012      | 2013                   | 2014                                                           | 2015  |       |

|--|-----------|-----------|-----------|------------------------|----------------------------------------------------------------|-------|-------|

|  | E-Beam    | 1 – 5     | 5 – 10    | 60 – 100*              | 100+*                                                          | 120+* |       |

|  | EUV       | 30 - 60   | 60 - 100  | 80 – 125               | 125+                                                           | 150+  |       |

|  | Immersion | 180 – 230 | 200 – 240 | 220 – 260              | 260+                                                           | 280+  |       |

|  |           |           |           | 22NM<br>VOLUME<br>RAMP | NECESSARY FOR IMME<br>DOUBLE / MULTI-PATTI<br>TO BE COST-EFFEC |       | ERNIN |

Resist Process Steps on Track

### SOKUDO Coat/Develop Track 22nm Process Development

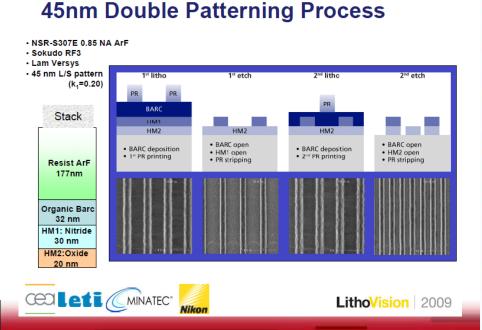

Cimec Double Patterning LPLE

Materials & Process Benchmarking 32nm → 26nm

• Selete EUV Lithography Resist Qual.

New resist process evaluations @ SELETE

• Celett E-Beam DW Qualification

MAPPER Lithography E-Beam Process R&D

SOKUDO RF3 track process E-Beam litho. exposures on Vistec SB3054DW at LETI

# imec Immersion Lithography with SOKUDO

- Immersion Resist Process Defectivity: Microbridging & Resist Filtration

- CoO Study for Double Patterning Lithography

- CDU optimization for immersion lithography & Double Patterning:

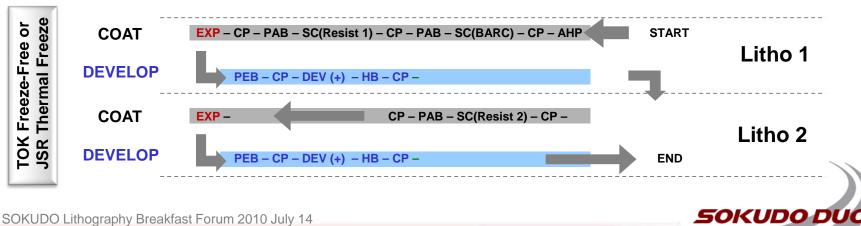

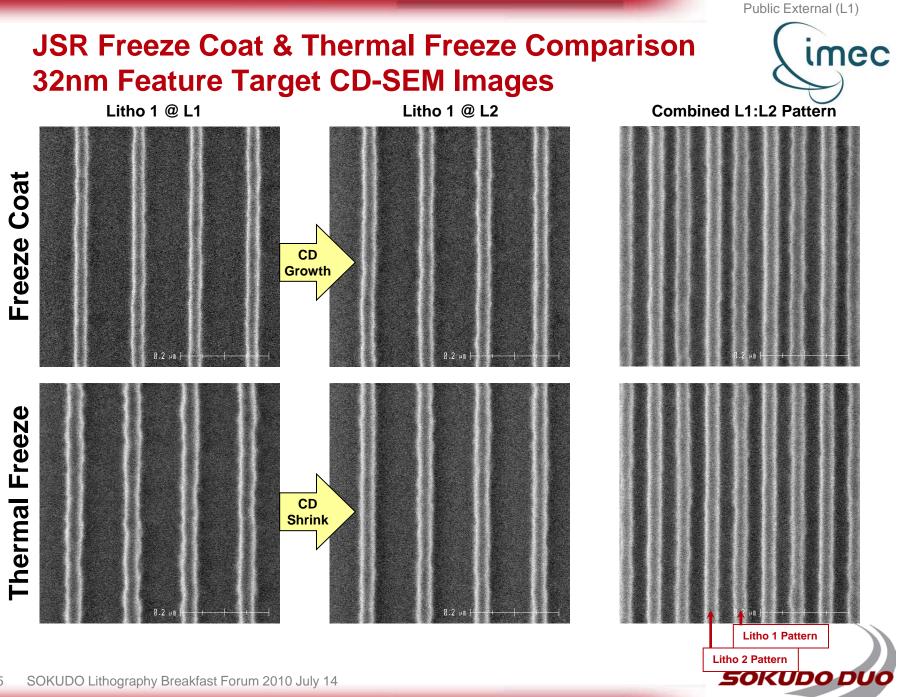

- JSR's litho-freeze-litho process (freeze coat, thermal freeze)

- TOK's posi-posi process "Freeze-Free"

### "Photo" Double Patterning Resist Process on Track

|                 | Freeze Coat<br>chemical b/w<br>1 <sup>st</sup> & 2 <sup>nd</sup><br>Resist | Self-Freeze by<br>2 <sup>nd</sup> Resist Coat<br>& Bake | Thermal freeze<br>bake |  |

|-----------------|----------------------------------------------------------------------------|---------------------------------------------------------|------------------------|--|

| JSR             | JSR                                                                        |                                                         | •                      |  |

| ток             |                                                                            | ۲                                                       |                        |  |

| Dow Elec. Mtrl. | 0                                                                          | 0                                                       |                        |  |

| Shin-Etsu       |                                                                            | 0                                                       |                        |  |

| Sumitomo        |                                                                            | 0                                                       |                        |  |

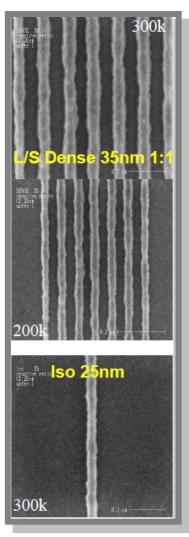

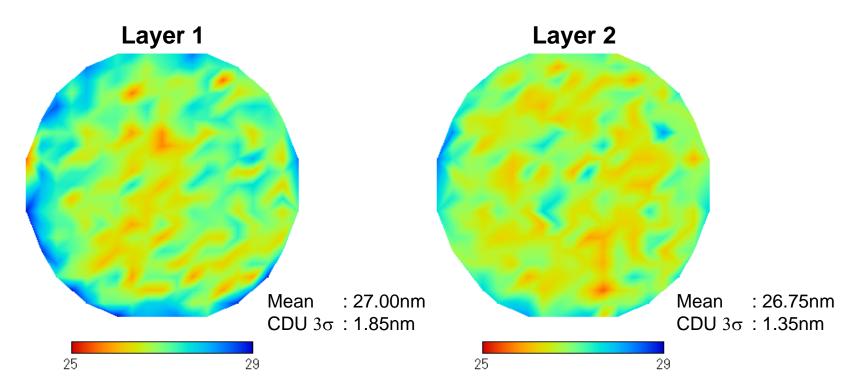

## **JSR Thermal-Freeze 26nm L/S Target CDU**

SPIE 7639-81 Simplified "Litho-Cluster-Only" solution for double patterning ; JSR, ASML, SOKUDO

The CD uniformity data with the thermal freeze process comparable to traditional litho-etch-litho-etch and spacer double patterning CDU.

Substrate:ARC®29-SR (105nm)

Layer 1 : Non-TC thermal freeze resist (FT=60nm,130C/125C, SCA/RCA/ACA=90<sup>o</sup> /76<sup>o</sup> /94<sup>o</sup>) Layer 2 : Non-TC normal resist (FT=50nm,100C/95C, SCA/RCA/ACA=92<sup>o</sup> /80<sup>o</sup> /95<sup>o</sup>), Exposure : 39nmL96nmP with att-PSM, NA=1.35, Dipole40X, 0.747/0.626, Y-Polarization Development : ECO Nozzle(OPD262/DIW)

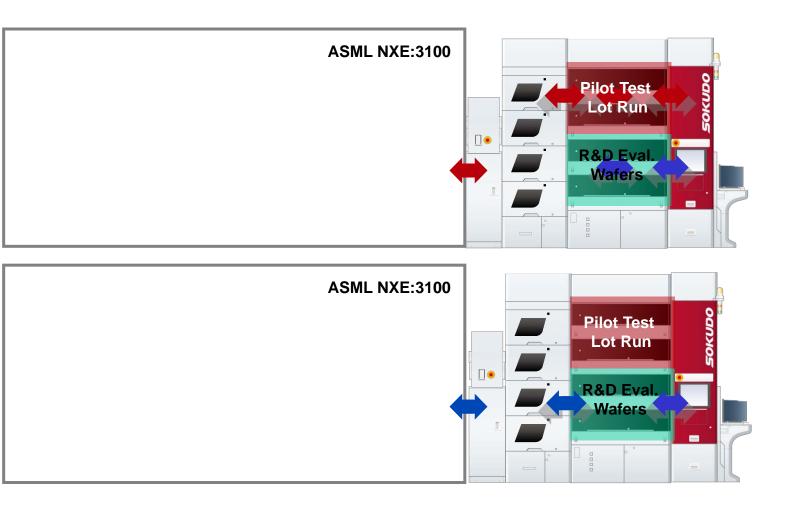

## **SOKUDO DUO** integration for ASML NXE:3100 (EUV)

#### SOKUDO EUVL Coat/Develop Track Configurations ~120wph

- Coat: Underlayer, Resist

- Develop: TMAH / TBAH developers; various rinse approaches

- Bake: Biased Hot Plate (QBH) for CDU control / tuning; "Q" Quick set-temperature change bake between lots

### Maximize EUV Lithocell Utilization: Exposure Test Lot Run + R&D Eval. Wafers simultaneously

Public External (L1)

#### Always keep critical EUV scanner running when available! **KEY for R&D + Pilot Line Productivity!** SOKUDO DU

SOKUDO Lithography Breakfast Forum 2010 July 14 20

## **E-Beam Experience by SOKUDO**

- Advantest F-100 (Japan)

- SOKUDO RF3 Coat, Developer in-line with E-Beam

- Vistec SB3054DW @ Celleti Grenoble (France)

- SOKUDO RF3 off-line for E-Beam

- in-line with Nikon NSR-S307

# The End Goal...

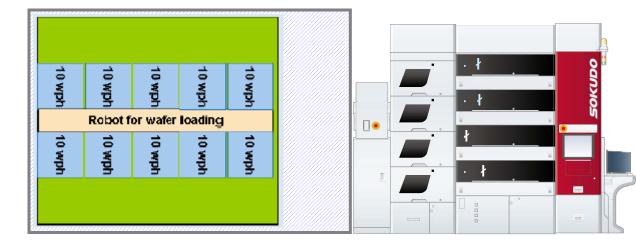

### **SOKUDO DUO** E-Beam Coat/Develop Track in-line with MAPPER

**MAPPER E-Beam Cluster**

Target 100 WPH

**SOKUDO DUO Track**

~%\$\$!%&\$`K D<

ł

2C = Underlayer 2C = RESIST4D = DEVELOPwith Backside Scrub + E-Beam interface

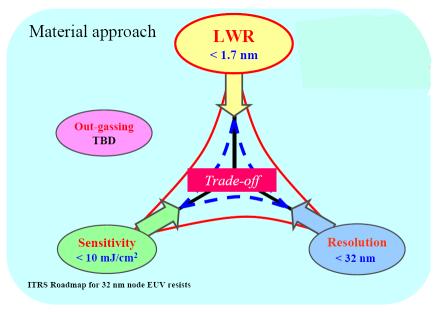

# EUV, E-Beam Common Resist Process Development Focus Points

- Resist Manufacturers Continuously Reformulating for

- Line Width Roughness (LWR)

- Sensitivity to Dose

- ► Resolution 32 nm → 22 nm

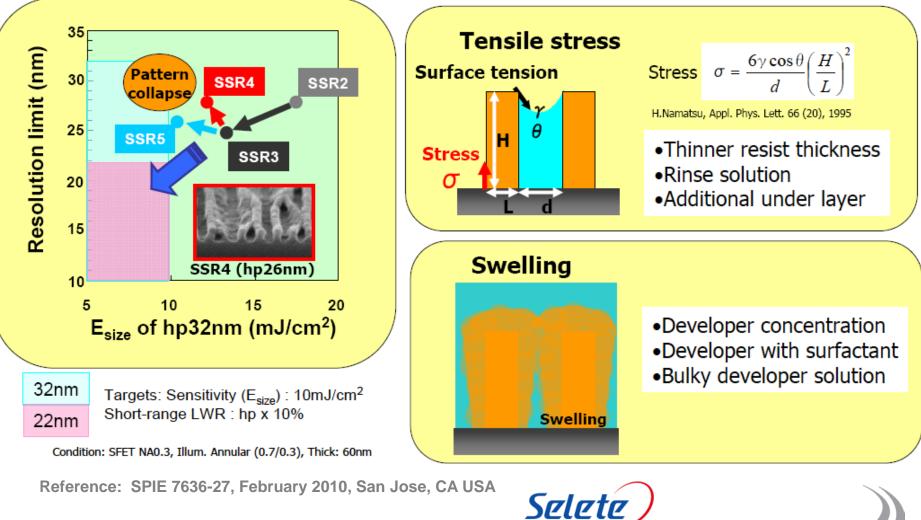

- 32 nm → 22 nm CD LWR, Pattern Collapse & Defectivity Track Process Studies:

- Develop methods, solutions

- Rinse methods, solutions

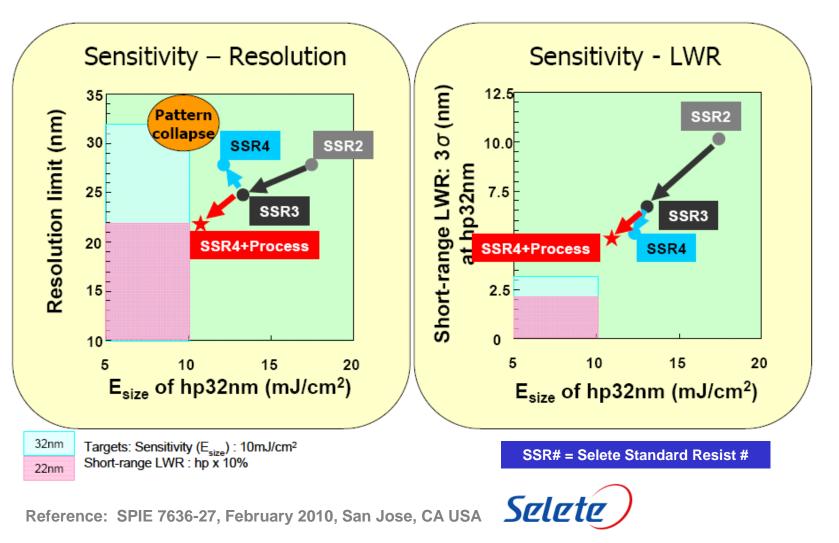

Reference: SPIE 7636-27, February 2010, San Jose, CA USA

# **SOKUDO EUVL Technical Papers History**

#### SPIE Advanced Lithography 2009

- 7273-111 **Development of EUV resists at Selete** SELETE (SOKUDO assignee, Koji Kaneyama)

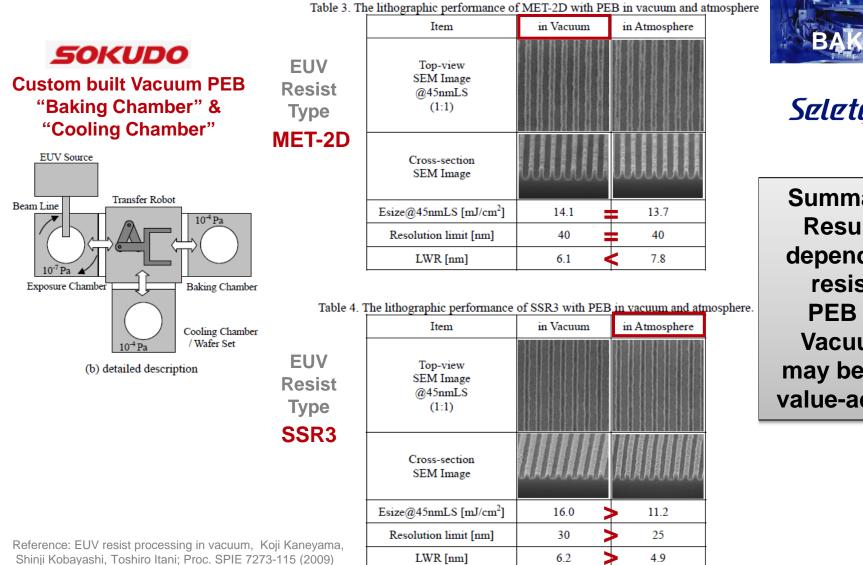

- 7273-115 **EUV resist processing in vacuum** SELETE, SOKUDO

#### International Symposium on EUVL 2009

- Resist II **EUV resist materials and processing at Selete** SELETE (SOKUDO assignee, Koji Kaneyama)

- Poster 94 Study of post-develop defect on typical EUV resist SOKUDO

#### SPIE Advanced Lithography 2010

- 7636-111 Study of post-develop defect on typical EUV resist SOKUDO

- 7636-115 Alternative resist processes for LWR reduction in EUVL SELETE (SOKUDO assignee, Koji Kaneyama)

- 7639-26 **Development of EUV-resists based on various new materials** SELETE (SOKUDO assignee, Koji Kaneyama)

- 7636-27 **Development of resist material process for hp 2x nm devices using EUV lithography** SELETE (SOKUDO assignee, Koji Kaneyama)

2009 International Symposium on Extreme Ultraviolet Lithography

## Coat, Bake & Develop Track Process Knobs for EUV / E-Beam resist development

# SPIN COAT

- Dispense Chemistries:

- Underlayer +

- Photo Resist

- Thin-film coating recipe

- 40-60nm thickness

# BAKE & CHILL

- ✤ Post-Expose (PEB) for

- CD Uniformity control

- ✤ High Temp. (PAB, BARC)

# DEVELOP

- Defect Control Approach

- ✤ Wafer Rinse & Dry

- Surfactant Rinse

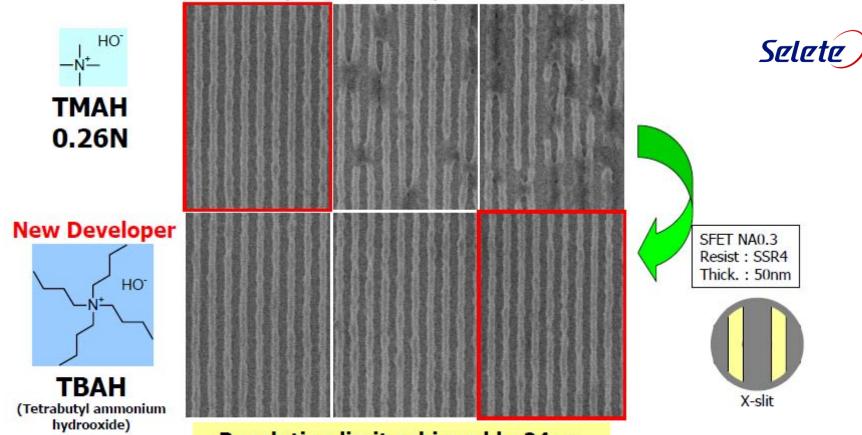

- Developer Chemistries:

TMAH, TBAH(?)

SOKUDO DUC

# **PEB** in vacuum vs. atmosphere

SOKUDO Lithography Breakfast Forum 2010 July 14

28

Public External (L1)

Selete

Summary: Results depend on resist, **PEB** in Vacuum may be low value-added

SOKUDO DU

## **TBAH Developer extends CD capability, reduces pattern collapse**

25nm L/S

24nm L/S

26nm L/S

Public External (L1)

SOKUDO DU

#### **Resolution limit achieved hp24nm**

Reference: EUV resist materials and processing at Selete, K. Matsunaga, et.al., International Symposium on EUV Lithography, October 2009, Prague

0.26N

SOKUDO DU

## Pattern Collapse limiting EUV resist resolution

### Sensitivity - Resolution

Model of pattern collapse and improvement by process

SOKUDO DU

### EUV resists improving with each new generation: Resolution, LWR, Sensitivity

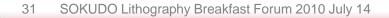

## **Common / specific defect history; EUV study started**

Selete

(e) of i

### EUV & E-Beam ...

- Although EUV may be leading the march towards 22 nm, E-Beam can close gap with (MAPPER) throughput plans for improvement towards 2012+

- SOKUDO participating in EUV and E-Beam collaborations

- EUVL consortia resist evaluations and characterization

- E-Beam IMAGINE project resist process qualification

### • EUV and E-Beam resists following similar trends and challenges:

- ► In parallel transitioning from  $32nm \rightarrow 22$  nm process development

- Both resist systems largely based on reformulating i/KrF generation blends

- Resist trending to thinner coatings: 40-60 nm target thickness

- Resolution LWR Sensitivity (RLS) all common issues

### "Shooting for the 22nm Lithography Goal" with the

SOKUDO Lithography Breakfast Forum 2010 July 14 (L1)