# Double Patterning Jumps the 200wph Hurdle: Coat/Develop Track Equipment

Charles Pieczulewski SOKUDO Lithography Breakfast Forum 2009 July 15

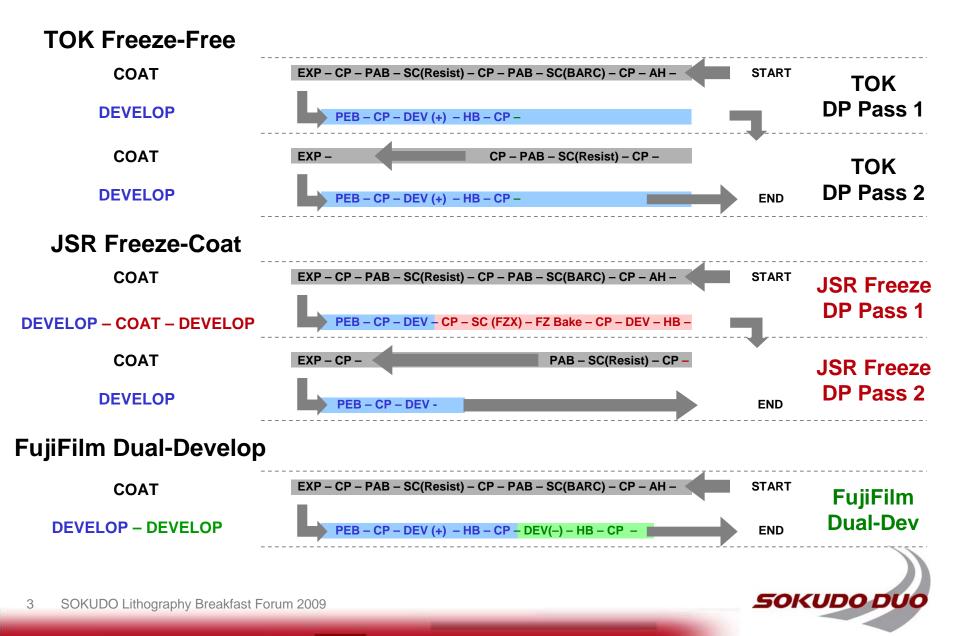

#### "Photo" Double Patterning Resist Process Options

|                                                    |             | Litho-Freeze<br>chemical b/w<br>1 <sup>st</sup> & 2 <sup>nd</sup><br>Resist | Self-Freeze<br>by 2 <sup>nd</sup> Resist<br>Coat & Bake | UV Cure<br>Freeze                                             | Negative<br>Tone Dev.<br>Resist              | Evaluation<br>Partners per<br>Technical<br>Papers |

|----------------------------------------------------|-------------|-----------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------|---------------------------------------------------|

|                                                    | JSR         | •                                                                           | 0                                                       | Δ                                                             |                                              | IMEC, Albany                                      |

|                                                    | ток         |                                                                             | •                                                       |                                                               | -                                            | Nikon, IMEC                                       |

|                                                    | FujiFilm    |                                                                             |                                                         |                                                               | Ð                                            | IMEC                                              |

|                                                    | Rohm & Haas | 0                                                                           | 0                                                       |                                                               |                                              | CEA-LETI                                          |

|                                                    | Shin-Etsu   |                                                                             | 0                                                       | Δ                                                             |                                              | AMD, Ushio,<br>Sokudo/<br>AMAT                    |

|                                                    |             | Complex Process<br>on Track but<br>Good Results !!!                         | Preferred but<br>Weak Results<br>(will improve)         | Needs More<br>R&D Effort<br>but Attractive<br>if it can work! | Potential for<br>Niche Apps.<br>(trench, CH) |                                                   |

| SOKUDO Lithography Breakfast Forum 2009 SOKUDO DUC |             |                                                                             |                                                         |                                                               |                                              |                                                   |

### "Photo" Double Patterning Resist Process Example

Myth: Semiconductor IC manufacturers only need one Double Patterning Solution that works for them

- Reality: One Double Patterning Solution will not cover all IC process pattern scenarios, will need <u>multiple</u> "photo" Double Patterning solutions:

- Dense lines (straight)

- Dense lines (elbow)

- Contact holes, dense / iso

- Trench patterns

- ► Etc.

Therefore... Coat/Develop Track needs flexibility to run <u>whatever</u> "Double Patterning Solution" that fits the IC process pattern layer

#### >200wph Double Patterning Requirements for Coat/Develop Track

• Flexibility to run <u>whatever</u> "Double Patterning Solution" that fits the IC process pattern layer

Coat/develop track should not limit options of manufacturer

- Maintain >200wph throughput even with extra process steps demanded by each Double Patterning solution

- Expandable to support adding coat, develop and bake units

- Enable multi-pass flows (i.e. two-step develop in one flow)

### Maintain continuous supply of wafers inside track: FOUP / Wafer Buffering

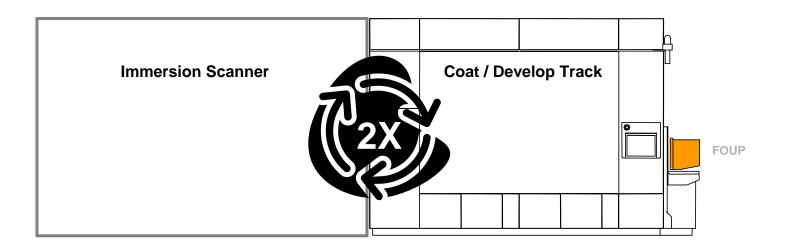

#### "Photo" Double Patterning = Two-Cycles Through Lithocell

#### Two-Cycle Wafer Flow Management Dilemma

- Semiconductor Fab Host reloads FOUP cassette for 2<sup>nd</sup> cycle or

- Track internally manages auto-start of second cycle/pattern and communicated to scanner via linked-litho network

SOKUDO DU

Solution: Clear protocol with fab host and track/scanner on second cycle DP wafer reloading

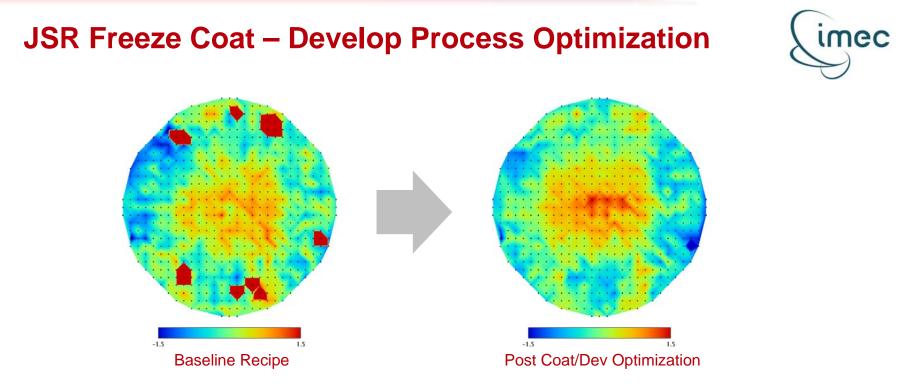

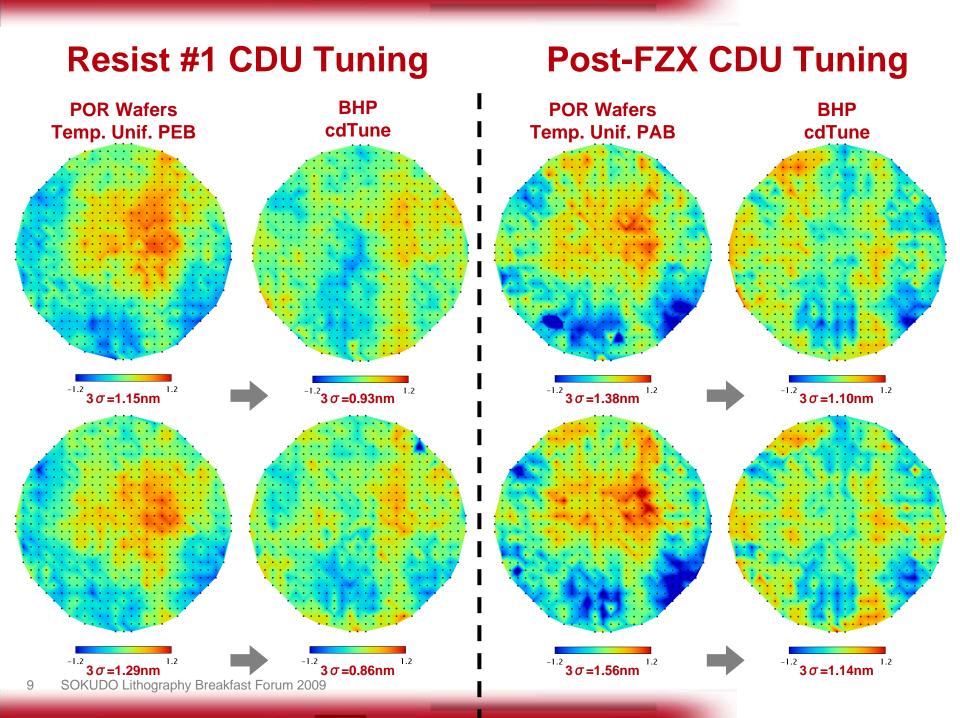

#### **SOKUDO 22nm Double Patterning Process Development at IMEC**

#### • CDU & Defectivity was Unacceptable with Initial Baseline Process

Freeze Material was Not Properly Removed due to Poor Wetting

#### • Coat & Develop Optimization Complete: CDU ~1.5nm 3 $\sigma$

- Defects from Remaining Freeze Material Resolved

- Next... Evaluated cdTune<sup>tm</sup> at Freeze PAB to Optimize CDU

- Model Predicts ~1nm 3 σ

#### All Results Single Pattern Only

8 SOKUDO Lithography Breakfast Forum 2009

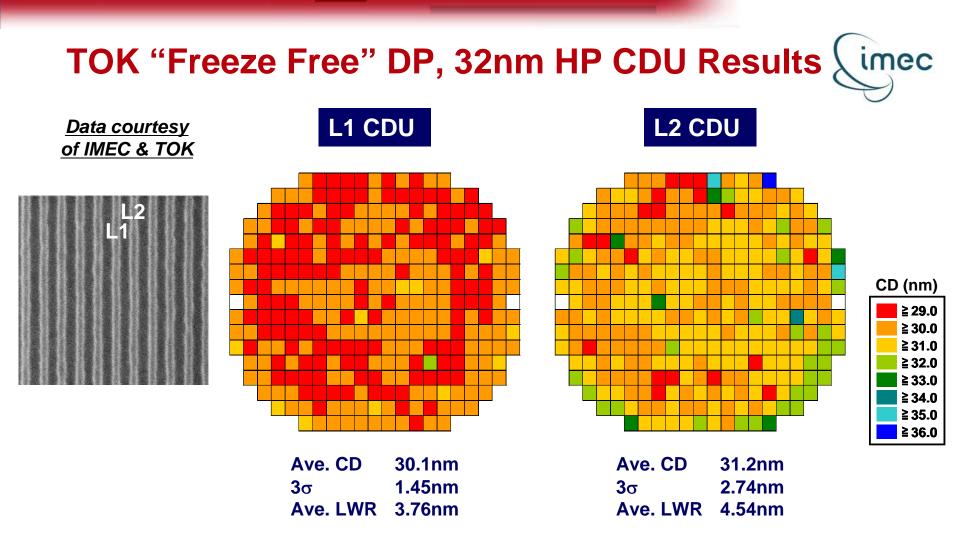

#### ◆ Target: 32nm DHP

Film thickness was optimized to prevent pattern collapsing

CDU indicated applicable value to further investigations

SOKUDO DUO

10 SOKUDO Lithography Breakfast Forum 2009

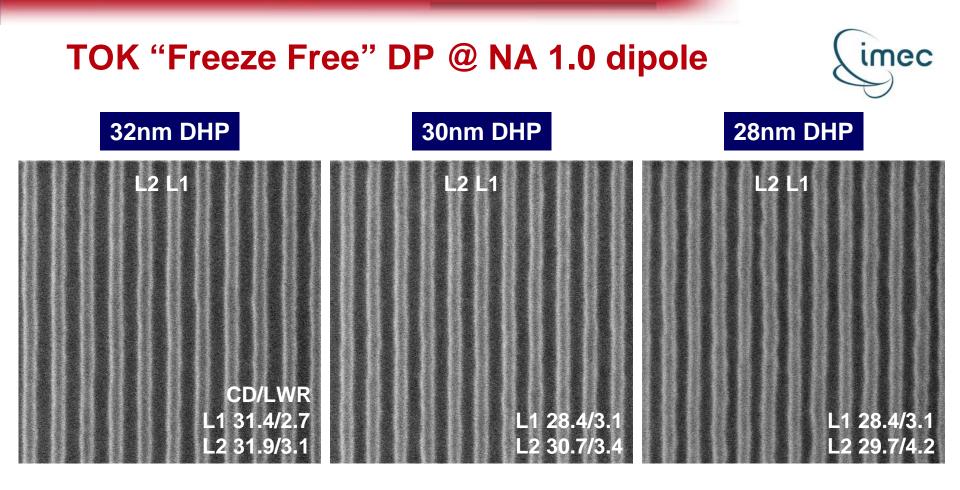

Target: 32nm DHP

Film thickness was optimized to prevent pattern collapsing.

$\rightarrow$  Thinner setting both 1<sup>st</sup> level resist and 2<sup>nd</sup> level resist.

30 & 28nm HP patterns were obtained utilizing dipole illumination.

Data courtesy of IMEC & TOK

SOKUDO DUO

## Key Message: SOKUDO DUO for Double Patterning

- SOKUDO DUO Immersion Track Qualifying @ 250wph

- SOKUDO DUO flexible to meet >200wph requirement for multiple Double Patterning Alternatives

- SOKUDO on the leading-edge of Double Patterning process know-how in collaboration with IMEC

For Further Information Please Contact: Charles Pieczulewski Senior Manager, Strategic Marketing SOKUDO Co., Ltd., Kyoto, Japan charles@sokudospeed.com