### Self-Aligned Double Patterning for 3xnm Flash Production

Chris Ngai Dir of Process Engineering & Lithography Maydan Technology Center Group Applied Materials, Inc. July 16<sup>th</sup>, 2008

SILCON SYSTEMS GROUP

External Use

### **Overview**

- Double Patterning Drivers for Flash

- Comparison of Double Patterning Schemes

- Applied Materials Self-aligned Double Patterning (SADP)

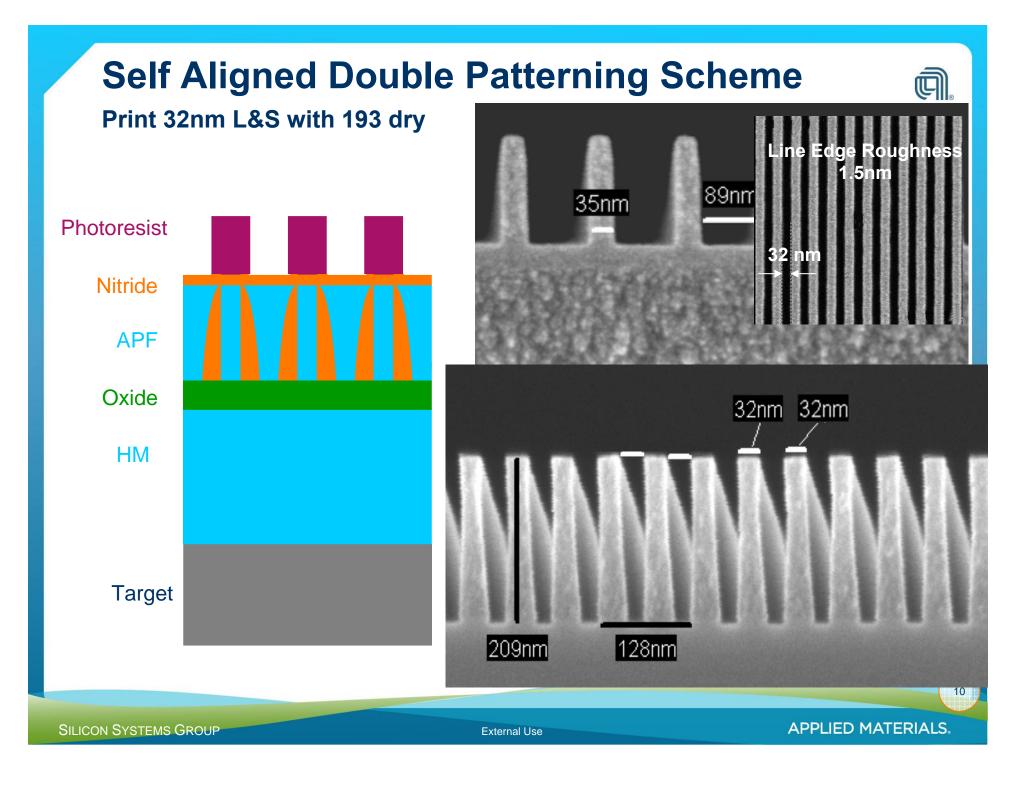

- SADP Approach & 32nm Demonstration

- SADP 22nm Extendibility

- Application Demonstration

- Production Proven Products for SADP Flash Manufacturers

#### Summary

# **Double Patterning Drivers**

External Use

APPLIED MATERIALS.

### **Drivers for SADP**

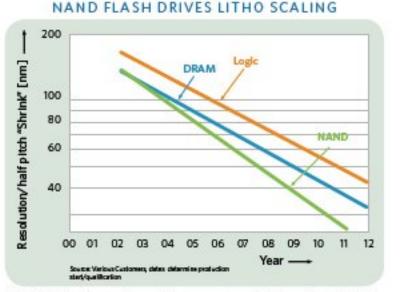

NAND Flash is driving the resolution requirements below 45nm by 2008. DRAM will follow one to two years later.

#### Flash - Aggressive half pitch needs

#### **Immersion Lithography – Resolution limitations**

Self-aligned double patterning (SADP) provides the capability to achieve aggressive half pitch at relaxed litho conditions

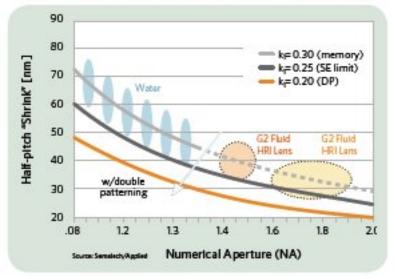

#### RESOLUTION BARRIER FOR SINGLE EXPOSURE

With 193nm exposure wavelength and current NA, double patterning is the only way to reach the required half-pitch for 32nm.

SILICON SYSTEMS GROUP

External Use

# **Double Patterning Schemes**

External Use

APPLIED MATERIALS.

| Double Patterning Approaches                   |                                                                                         |                                                                                        |                                                                      |  |  |  |

|------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|

| Туре                                           | Double Imaging                                                                          | Double Patterning                                                                      | Self Aligned Double<br>Patterning                                    |  |  |  |

| Process Flow                                   |                                                                                         | 1 <sup>st</sup> Exposure<br>Resist<br>BARC<br>HM<br>Device<br>2 <sup>nd</sup> Exposure |                                                                      |  |  |  |

|                                                | <ul><li>Coat Expose Develop</li><li>Resist Freeze</li><li>Coat Expose Develop</li></ul> | 2 Exposure                                                                             | <ul> <li>One critical exposure</li> <li>Spacer Technology</li> </ul> |  |  |  |

| Overlay<br>(Requirement:<br><3nm)              | ~ 6-8nm                                                                                 | ~ 6-8nm                                                                                | not applicable                                                       |  |  |  |

| <b>CDU</b><br>(Requirement: <3-4nm)            | Line - 2nm<br>Space – 3.7nm (w/o Overlay)<br>Space – 5.1nm1 (w/ Overlay)                | Line - 2nm<br>Space – 3.75nm (w/o Overlay)                                             | Line < 1.5nm<br>Space < 3.0nm<br>(1 population combining S1 & ,S2)   |  |  |  |

| Line Edge<br>Roughness<br>(Requirement: <3-4nm | ~ 4-5nm                                                                                 | ~ 3-4nm                                                                                | < 2nm<br>(Applied process)                                           |  |  |  |

| 6                                              |                                                                                         |                                                                                        |                                                                      |  |  |  |

| SILICON SYSTEMS GROU                           | P                                                                                       | External Use                                                                           | APPLIED MATERIALS.                                                   |  |  |  |

| SADP Scheme Comparisons      |                                       |                                                            |                                               |  |  |  |  |

|------------------------------|---------------------------------------|------------------------------------------------------------|-----------------------------------------------|--|--|--|--|

| Process<br>Scheme<br>Metrics | Negative<br>Line by Fill<br>Poly Core | PR/SOH<br>Positive<br>Line by Spacer<br>Resist or SOH Core | APF<br>Positive<br>Line by Spacer<br>APF Core |  |  |  |  |

| CDU, 3σ<br>Line/Core/Gap     | Good for trench                       | Good for line                                              | Good for line<br>1.1 / 1.7 / 2.4nm            |  |  |  |  |

| LER                          | Poly ~3.5nm                           | Same as PR                                                 | <2nm                                          |  |  |  |  |

| Core Mech<br>Integrity       | Good                                  | Poor                                                       | Good                                          |  |  |  |  |

| Materials<br>Selection       | Thermal budget, gapfill,<br>spacer SC | New Materials for PR and Spacer, thermal budget            | Known films (APF, PE<br>Spacer)               |  |  |  |  |

| Defectivity                  | High (Poly Etchback)                  | Low                                                        | Low<br>(Defect gallery in dev)                |  |  |  |  |

| Extendibility<br>to 2xnm     | Gapfill issue                         | PR height & integrity                                      | Demonstrated to 2x                            |  |  |  |  |

### **SADP: Memory Makers' Production Choice**

Solid State Technology

October 23, 2007 - Samsung Electronics Co. Ltd. says it has developed 64Gb multilevel cell NAND flash memory chip using 30nm process technology, built using double-patterning lithography, with commercial chips ready in about a year.

The new device utilizes a process called "self-aligned double patterning technology" (SaDPT), an upgrade from charge trap flash that Samsung has used for NAND flash on silicon nitride. in SaDPT, the first pattern transfer is a wider-spaced circuit design of the target process technology, then a second pattern transfer fills in the spaced area with a more closely designed pattern (see figure).

Samsung says it will use SaDPT with "existing photolithography equipment" for production using the 30nm process technology, targeting commercial production in 2009. In addition to the 64Gb MLC device, it has also built a 32Gb single-level cell NAND flash chip. Up to 16 64Gb flash devices can

be combined into a 128GB MP3 music files, the compa

Top Story: Lithography is among top productivity challenges Semiconductor International

hynix Semiconductor

November 8, 2007 -- Lithography is among the top productivity challenges facing the semiconductor industry, but packaging and testing costs are another area that must be addressed, according to Jin Seog Choi, chief technology officer at Hynix Semiconductor Inc. (Icheon, South Korea).

AMSUNG

In a panel presentation at the International Trade Partners Conference (ITPC), held this week in Maui, Hawaii, Choi addressed the future technologies needed to keep cost reductions on track.

Starting in 2009, when NAND devices are using 30-35 nm design rules and DRAM is in the 43-48 nm range, the memory manufacturers face critical lithography choices. Extreme ultraviolet (EUV) lithography offers a low k1 factor, but it is unclear when EUV will be ready for high-volume manufacturing. **Spacer patterning technology could be used for NAND memories** or double patterning lithography may be required, for both DRAM and NAND devices.

However, double patterning "has a high cost of ownership. The low throughput of double patterning is a key issue," Choi said...

#### Major NAND Flash Manufacturers have adopted SADP scheme as the baseline for 3xnm critical layers module development

SILICON SYSTEMS GROUP

External Use

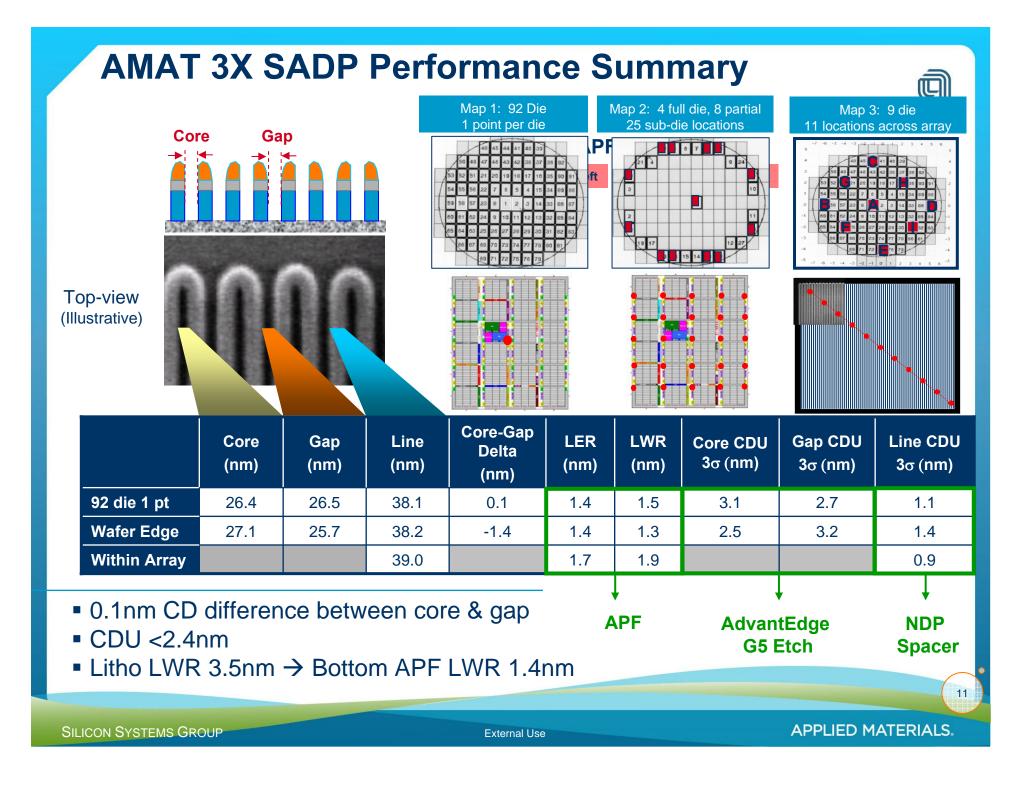

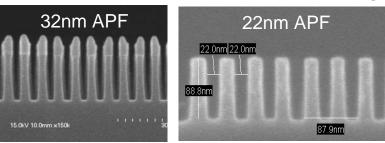

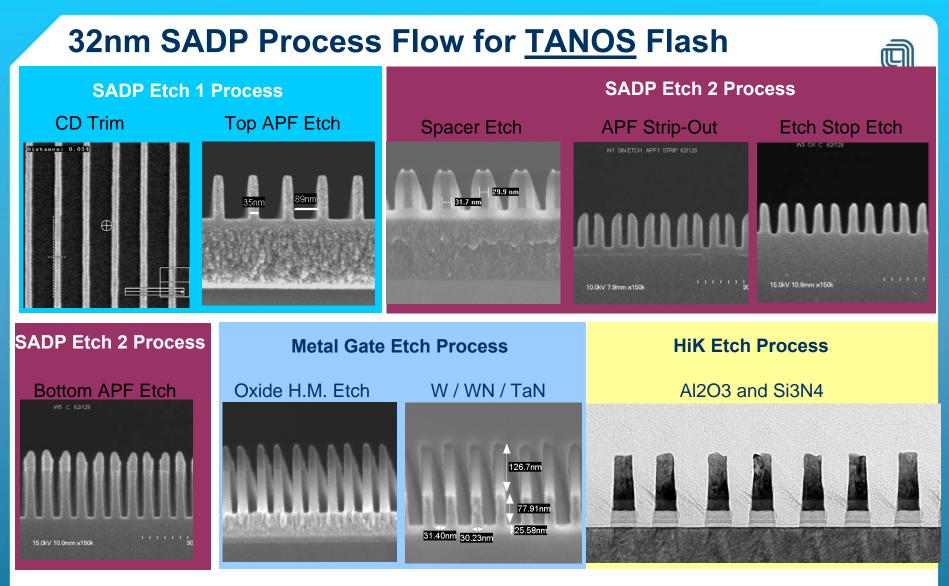

### 32nm and 22nm APF based SADP

APF Properties: Integrity, Alignment SADP Scheme Performance, LER CDU: Line vs Space

SILICON SYSTEMS GROUP

External Use

**APPLIED MATERIALS**

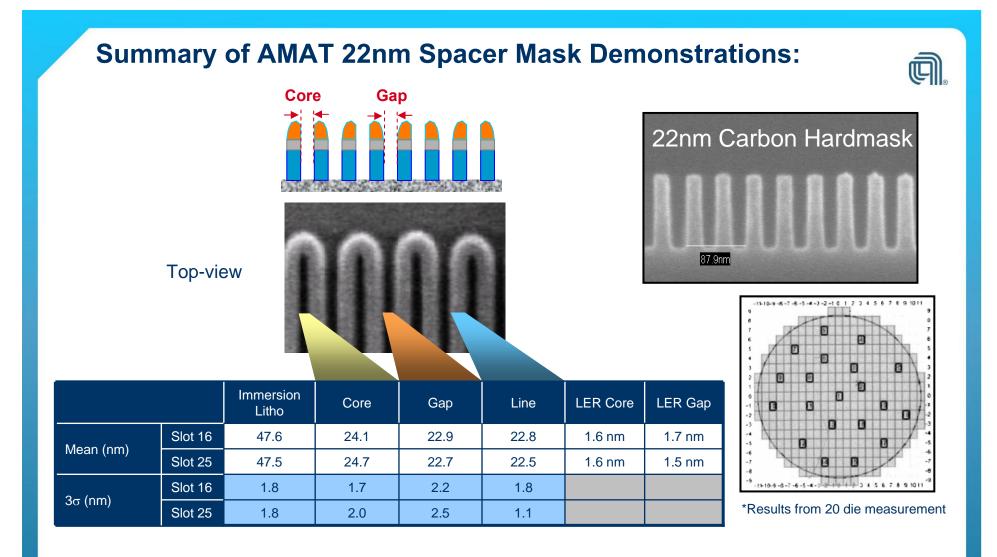

# 22nm Extendibility

External Use

APPLIED MATERIALS.

#### **Demonstrated extendibility to 22nm**

- CD Control of 2nm (3σ)

- LER <2nm</p>

SILICON SYSTEMS GROUP

External Use

APPLIED MATERIALS.

# **Application Demonstration**

External Use

APPLIED MATERIALS.

### **Applied Materials SADP Demonstrations**

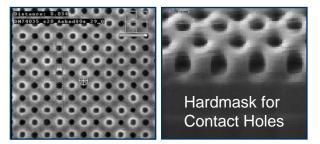

#### **Demonstrated Hardmask Patterning**

#### **Demonstrated Applications:**

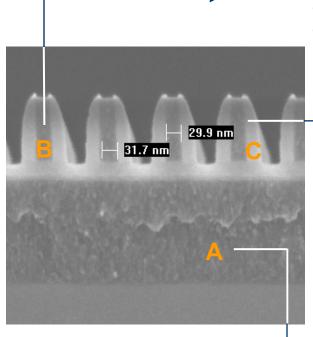

#### 34nm Self Aligned Dense Contact HM

Demonstrated on Flash critical dimension applications

SILICON SYSTEMS GROUP

External Use

**APPLIED MATERIALS.**

15

U

- AMAT AdvantEdge etch chamber was used for all patterning etch steps

- SADP only required 2 etch steps for patterning

SILICON SYSTEMS GROUP

External Use

APPLIED MATERIALS.

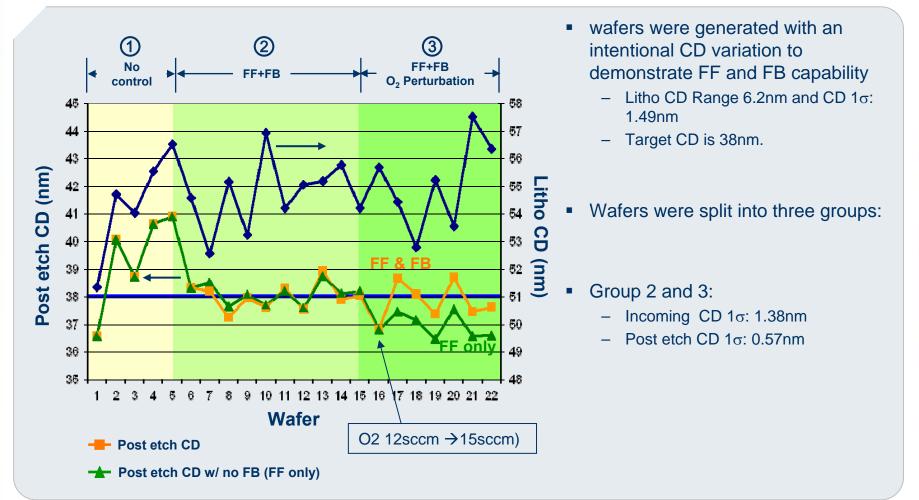

### **Core APF Automatic Process Control (APC) on G5** FF and FB Control (Litho -> Trimming/BARC/APF Core Etch)

Demonstrated WTW CD control of 1.5% of target CD, despite intentional incoming CD variation and  $O_2$  flow perturbation.

SILICON SYSTEMS GROUP

External Use

# **AMAT SADP Products**

External Use

APPLIED MATERIALS.

## AMAT is ready for patterning 32nm & beyond m

Technologies available on proven manufacturing platforms to reduce risk and time to market

| Producer <sup>®</sup> APF™ | AdvantEdge™ | UVision <sup>®</sup> SP | VeritySEM™ |

|----------------------------|-------------|-------------------------|------------|

| NDP™ PECVD                 | G5 Etch     | Brightfield             | Metrology  |

|                            |             |                         |            |

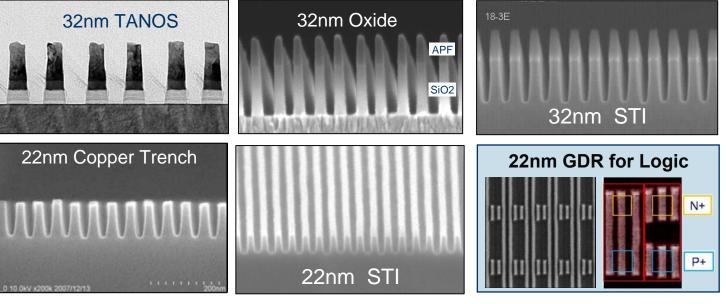

- Demonstrated Spacer Self-Align Double Patterning

- 32nm Lines & Spaces with TANOS Stack, STI, oxide

- 22nm Lines & Spaces with oxide & gridded STI structures

- Achieved:

- LER [<1.7nm]</li>

- CD Uniformity [<2nm]

- Overlay [<3nm]</li>

#### SADP is ready today for 32nm production Extendibility to 22nm is proven

SILICON SYSTEMS GROUP

External Use

# **Summary**

External Use

APPLIED MATERIALS.

### **SADP: Spacer Mask Approach**

#### **APF Core**

- Good LER

- Ashable no wet clean required

- Stable at high temp spacer temp requirement relaxed as a result

#### **NDP Spacer**

- >80% step coverage

- Good uniformity

- Good long range micro-loading performance

#### G5 for all SADP etch steps

- All-in-one chamber for all SADP etch steps & pattern etch

- Good CDU

- High productivity no warmup necessary

#### APF Hardmask

- Good LER of 2nm

- Good line bending resistance 5:1 at 32nm; 4:1 at 22nm

Full Portfolio Of Products Available For SADP Integration Schemes -

Including UVision for defect analysis and Verity for CD measurement

SILICON SYSTEMS GROUP

External Use

# think it. apply it."

APPLIED MATERIALS.