# **Double Patterning Material Solutions**

Sokudo/SEMI Lithography Breakfast Forum - 2008 Mark Slezak

### Background:

CTO JSR

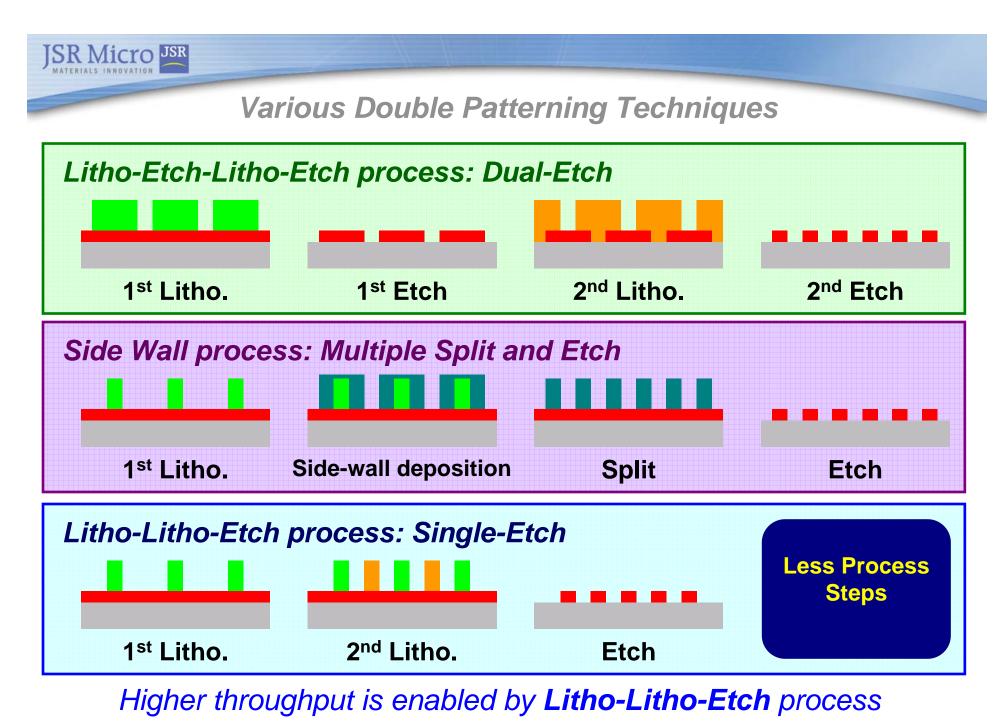

- Various Double Patterning Techniques

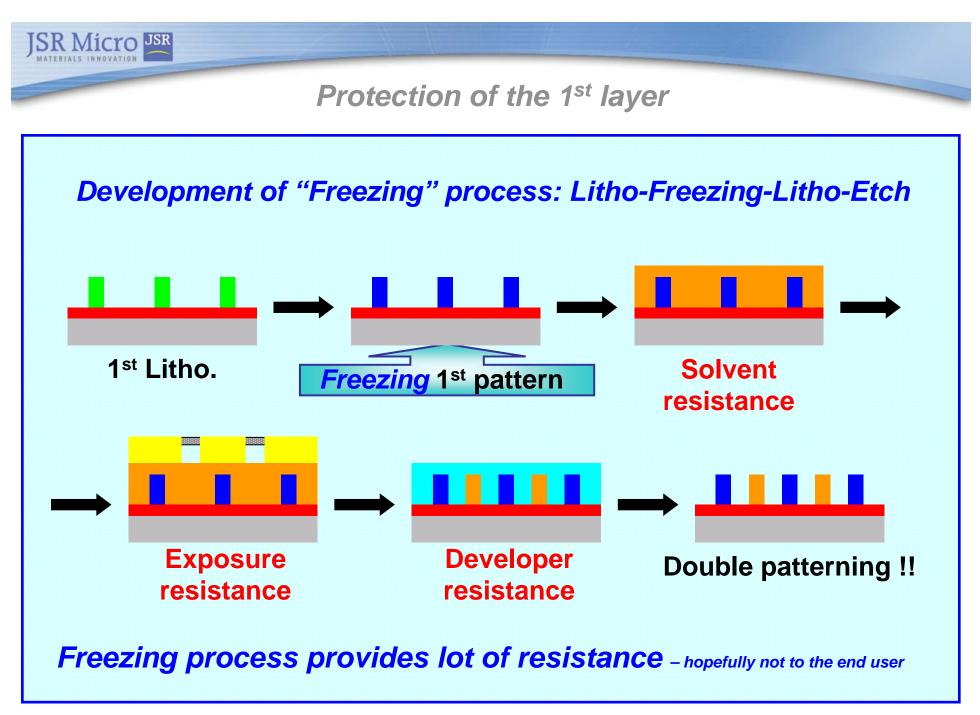

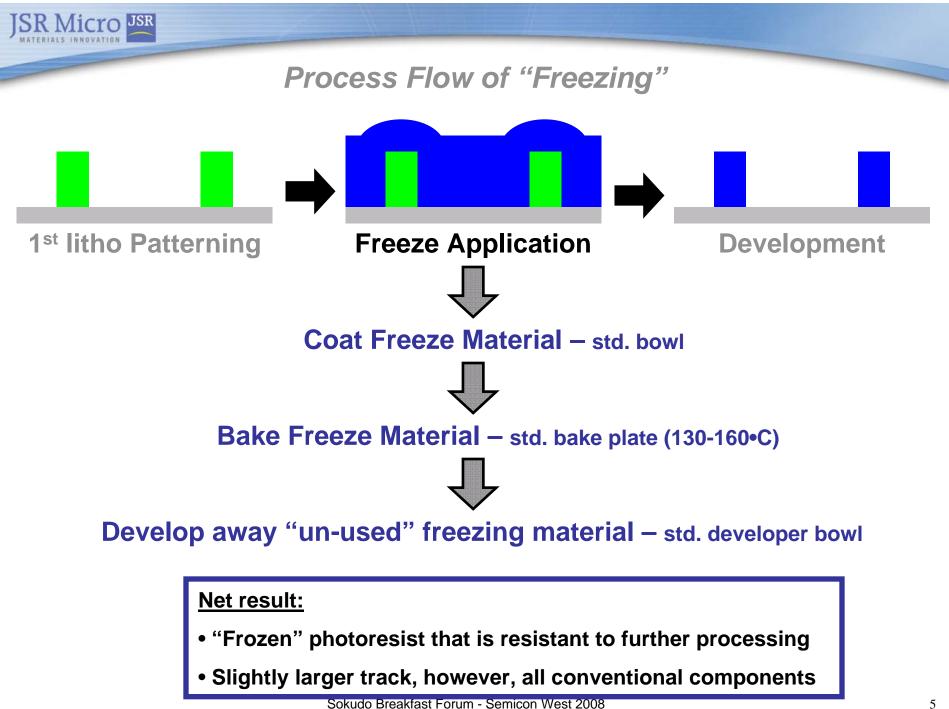

- Resist Freeze Process

# Lithography performance of JSR Freeze Process

- 32nm LS formation and etching

- "Freezing" process for 2-D logic patterning

- Contact Hole formation by "Freezing" process

- Summary

Background:

SR Micro JSR

- Various Double Patterning Techniques

- Resist Freeze Process

# Lithography performance of JSR Freeze Process

- 32nm LS formation and etching

- "Freezing" process for 2-D logic patterning

- Contact Hole formation by "Freezing" process

- Summary

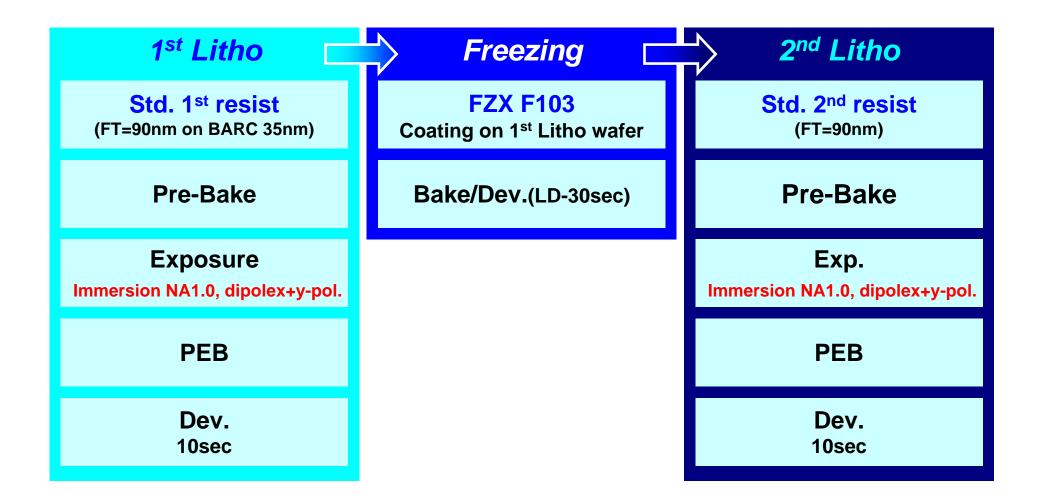

**Experimental Condition**

JSR Micro JSR

### Formation of 32nmLS Pattern

JSR Micro JSR

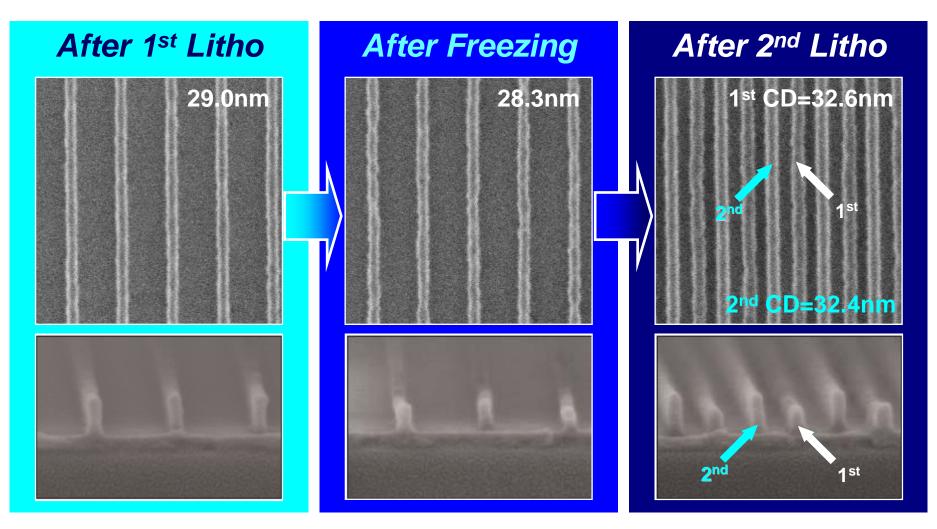

#### Formation of 32nmLS double patterning

**JSR Micro** JSR

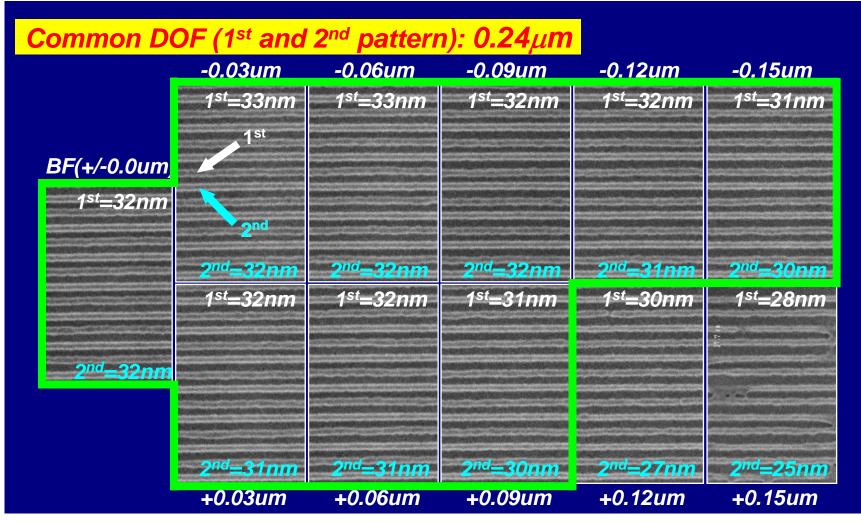

After 2<sup>nd</sup> litho, 240nm common DOF in both 1<sup>st</sup> and 2<sup>nd</sup> litho patterns of 32nmLS was obtained

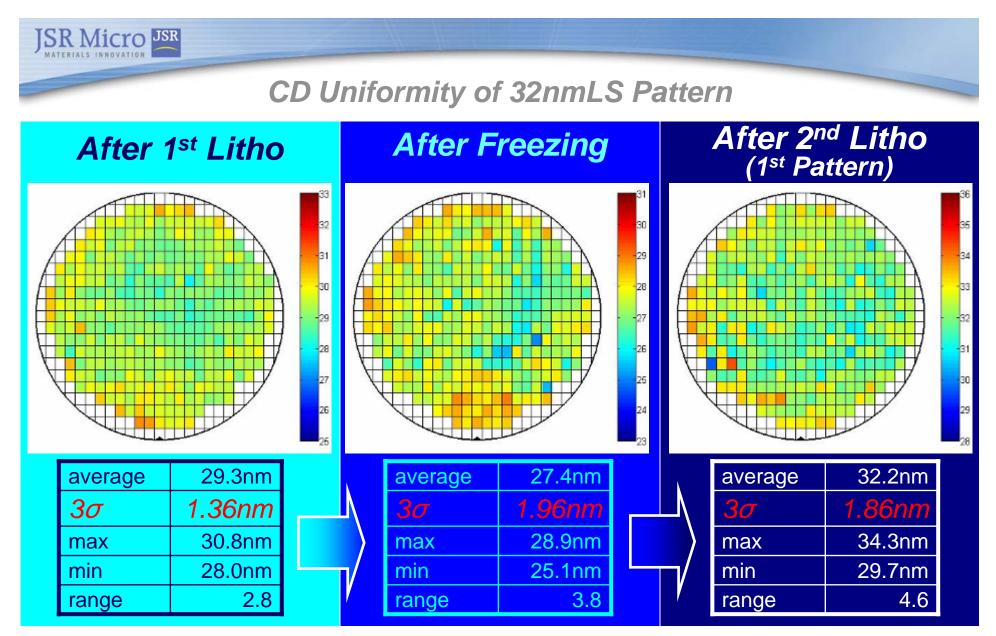

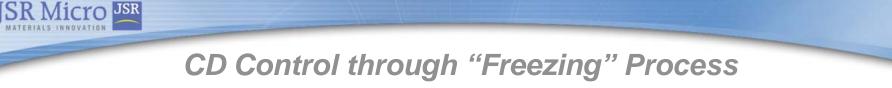

CD uniformity of 1<sup>st</sup> litho pattern was kept within 2nm through double patterning step with freezing process

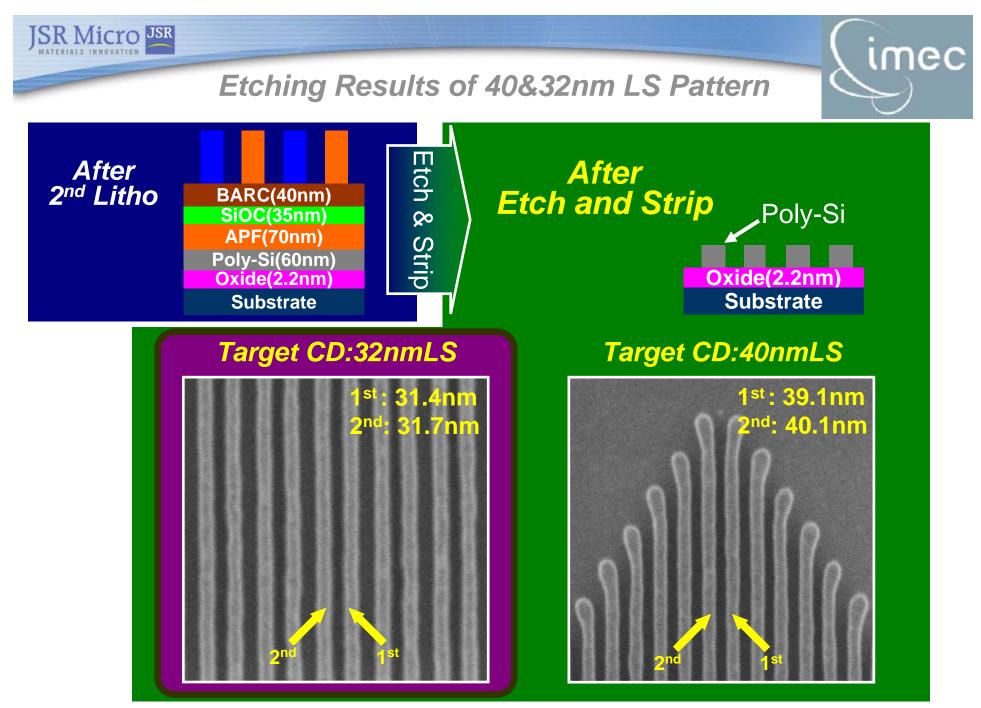

**Etching Experiment for "Freezing"**

#### ≻Materials

- 1<sup>st</sup> resist: JSR standard resist (FT=120nm(40nmL80nmP)/90nm(32nmL64nmP))

- Freezing materials: FZX F103

- 2<sup>nd</sup> resist: **JSR standard resist** (FT=90nm)

#### >Organic/Inorganic stack

BARC : 40nm / SiOC:35nm / APF : 70nm / Poly : 50nm / Oxide : 2.2nm BARC(ARC160:40nm) SiOC(35nm) APF(70nm) Poly-Si(60nm) Oxide(2.2nm) Substrate

### Target CD & Exposure/Illumination condition

- 40nmLS: NA=1.2, Annular(0.8/0.5) + xy-pol.

- <u>32nmLS</u>: NA=1.0, Dipole40 + pol.

Background:

SR Micro JSR

- Various Double Patterning Techniques

- Resist Freeze Process

# Lithography performance of JSR Freeze Process

- 32nm LS formation and etching

- "Freezing" process for 2-D logic patterning

- Contact Hole formation by "Freezing" process

- Summary

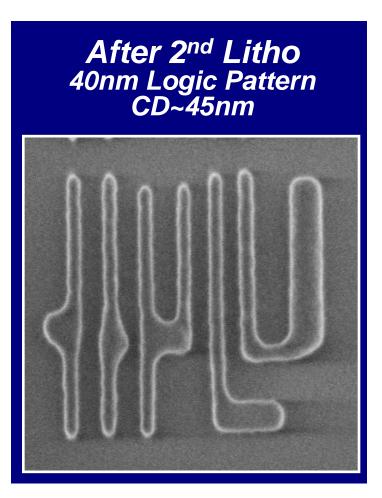

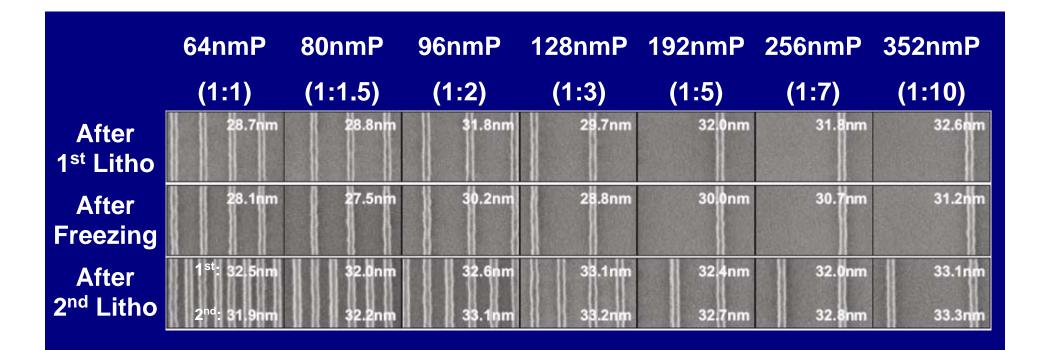

### "Freezing" Process for 2D Logic Patterns

> Can we handle 2D logic patterning with "Freezing" process?

✓ For complex 2D application, the pitch dependency of freezing process on 1<sup>st</sup> pattern CD variation is important.

> Freezing technique works well for 32nm various pitch patterns.

Freezing technique is also available for complex 2D pattern.

Configuration of litho pattern was kept after etching.

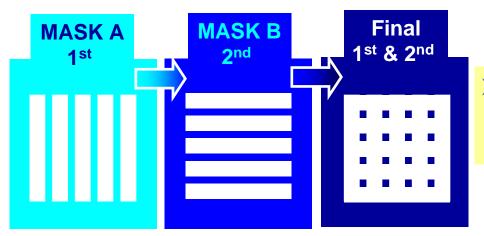

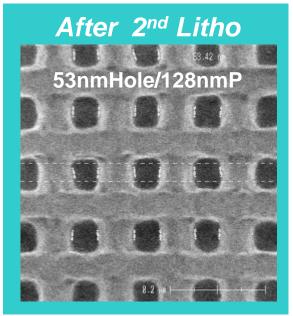

### **Cross-Lines CH Double Patterning**

#### Hole feature can be generated by using x/y-cross lines method with freezing process.

**Exposure/Illumination** NA=1.2, Ann(0.8/0.5)+xy-pol.

Sokudo Breakfast Forum - Semicon West 2008

imec

# Summary

- Resist "Freezing" processes have been developed for Litho-Litho-Etch double patterning applications

- ✓ 32nm half-pitch, 2-D logic patterns, and even contact hole patterns have been imaged using the resist freeze process

- ✓ Etch work through our partners at IMEC show excellent image transfer using materials that were processed with the freeze materials

- Resist Freeze is an elegant way of reducing process complexity and cost.