#### **High Throughput Maskless Lithography**

Sokudo lithography breakfast forum

July 14<sup>th</sup> 2010

Bert Jan Kampherbeek, VP Market Development and co-founder

## Agenda

- MAPPER's Objective

- MAPPER's Status

- MAPPER's Roadmap

...

.....

# MAPPER's objective: Provide lithography solution for 32 nm hp and beyond

- Provide 10 wph lithography unit in ~ 1  $m^2$  per unit at a competitive price

- Cluster several 10 wph units together, for example 10 units for 100 wph

- Application of first generation MAPPER manufacturing machines:

- Contact and via layers, 32 nm hp (22nm logic node)

- Metal layers, 32 nm hp

- Cutting / filling layers in double patterning, 16 nm hp (11nm logic node)

- MAPPER solution is extendable to at least:

- 16 nm hp random patterning @ 10 wph in 1 m<sup>2</sup>

- 8 nm hp with pitch division and cut/fill @ 10 wph in 1 m<sup>2</sup>

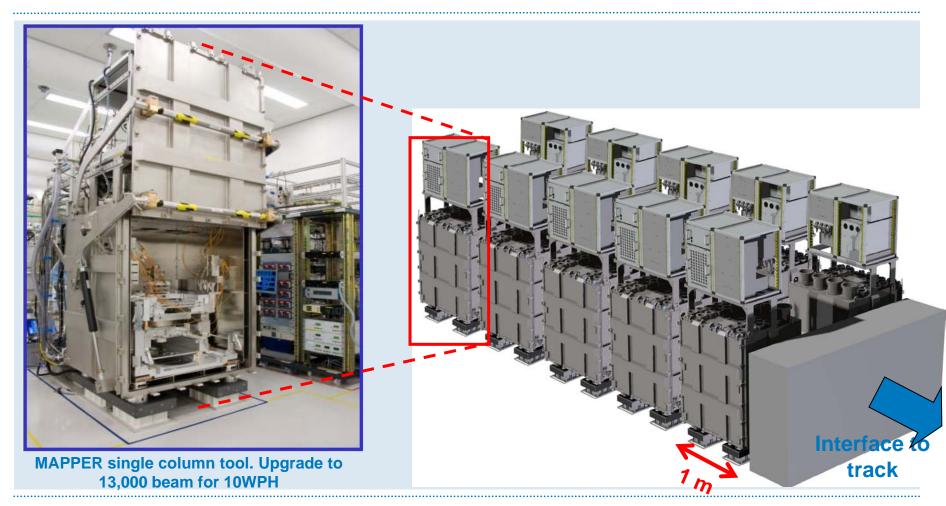

## MAPPER builds a system with 13,000 parallel electron beams for 10 wph

| Electron source                                                                    | Key numbers 22nm node:                                                     | HVM                                 | pre-alpha                        |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------|----------------------------------|

| Collimator lens                                                                    | #beams and data channels<br>Spotsize:<br>Beam current:<br>Datarate/channel | 13,000<br>25 nm<br>13 nA<br>3.5 Gbs | 110<br>35 nm<br>0.3 nA<br>20 MHz |

| Condensor lens ar                                                                  | Acceleration voltage                                                       | 5 kV<br>30 μC/cm²                   | 5 kV<br>30 μC/cm <sup>2</sup>    |

| Beam Blanker array<br>Beam Stop array<br>Beam Deflector arr<br>Projection lens arr | Pixel size @ nominal dose                                                  | 10 wph<br>3.5nm<br>Scanning         | 0.002 wph<br>2.25 nm<br>Static   |

# Tool cluster for 100 wph

# Application for MAPPER's technology (Logic example)

Assuming four critical metal layers at 22 nm:

|               | Direct patterning | Cutting | Position w.r.t. ArFi |

|---------------|-------------------|---------|----------------------|

| Gate layer    |                   | Х       | Complementary        |

| Contact layer | Х                 |         | Alternative          |

| Metal 1       | Х                 | Х       | Complementary        |

| Via 1         | Х                 |         | Alternative          |

| Metal 2       | Х                 | Х       | Complementary        |

| Via 2         | Х                 |         | Alternative          |

| Metal 3       | Х                 | Х       | Complementary        |

| Via 3         | Х                 |         | Alternative          |

| Metal 4       | Х                 | Х       | Complementary        |

| Via 4         | Х                 |         | Alternative          |

Applicable to at least 10 critical layers

## Agenda

- MAPPER's Objective

- MAPPER's Status

- MAPPER's Roadmap

...

#### **Overview current MAPPER machine**

- 1.3 x 1.3 m footprint containing 300 mm wafer stage

- Electron optics is completely in vacuum

- Source used for CRT application

- Lens arrays manufactured with MEMS techniques

- Wafer stage is in vacuum

- Long stroke motors outside shielding

- Short stroke magnetically shielded

- Data path is in the sub-fab (not in picture)

- Blanker chip with integrated photodiodes switches electron beams

- Data path connected through fibers with electron optics

## Two tools shipped for enabling infrastructure development

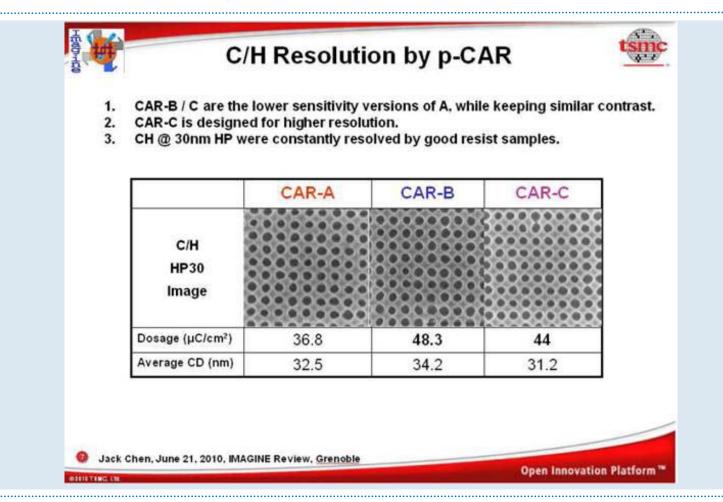

# Results of MAPPER prototype tool @ TSMC (1/2)

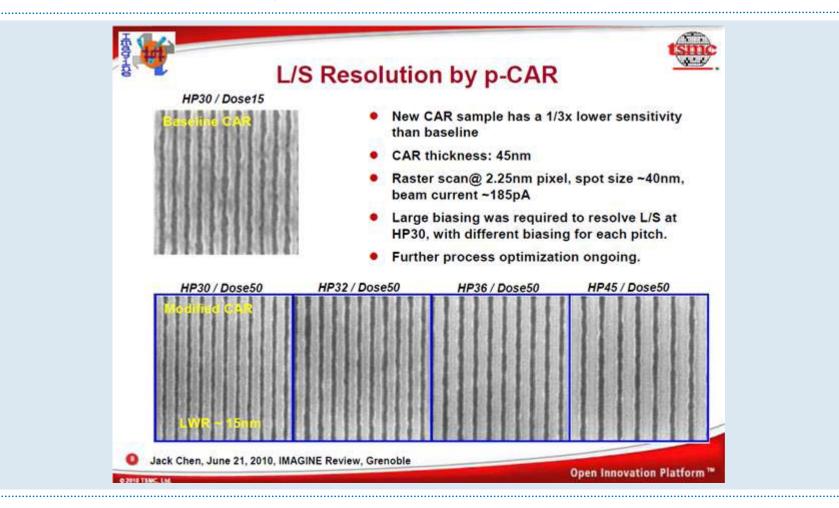

### Results of MAPPER prototype tool @ TSMC (2/2)

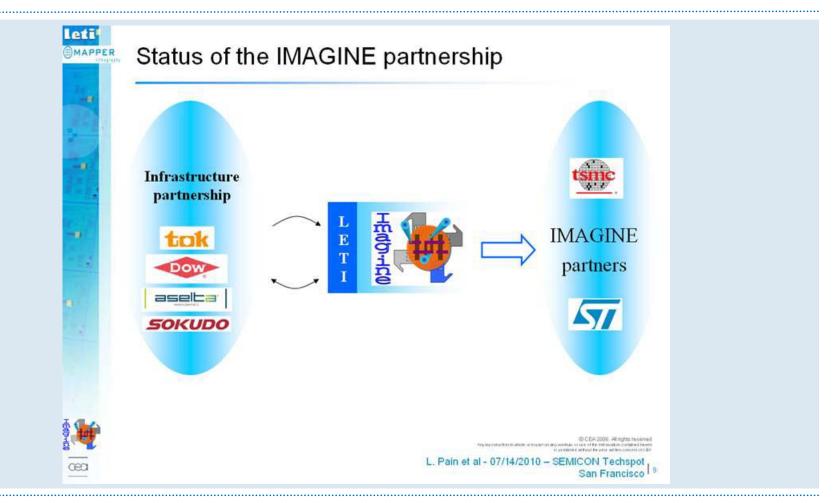

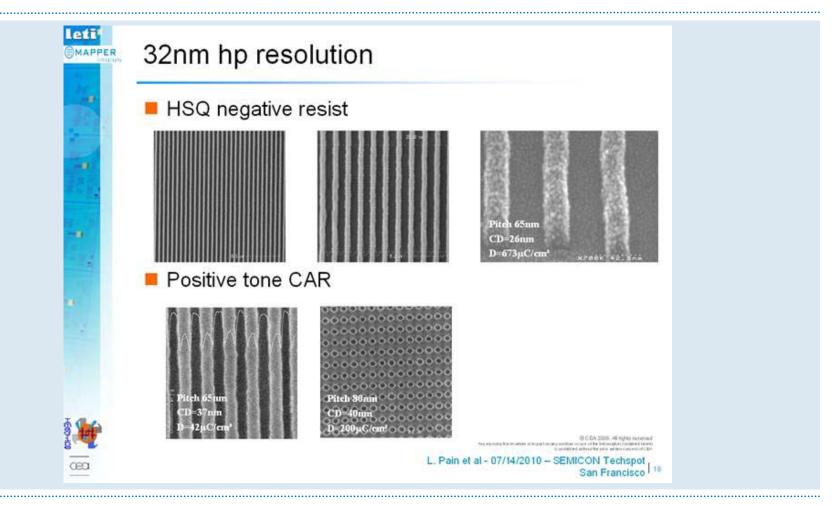

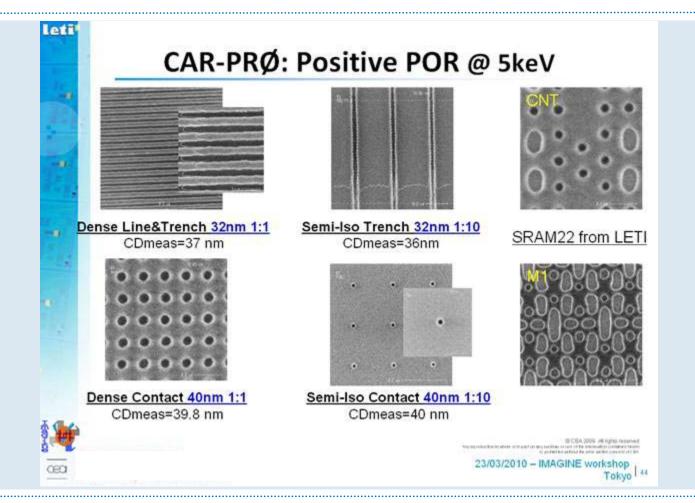

## Results of MAPPER prototype tool @ CEA-Leti (1/4)

#### Results of MAPPER prototype tool @ CEA-Leti (2/4)

#### Results of MAPPER prototype tool @ CEA-Leti (3/4)

#### Results of MAPPER prototype tool @ CEA-Leti (4/4)

## Agenda

- MAPPER's Objective

- MAPPER's Status

- MAPPER's Roadmap

MAPPER Roadmap

## Key technical challenges in scaling towards 10 wph and HVM

|                      |                       | Pre-alpha<br>status                               | HVM<br>requirement                               | Solution                                        |

|----------------------|-----------------------|---------------------------------------------------|--------------------------------------------------|-------------------------------------------------|

| Data<br>path         | Pattern<br>streaming  | 110 beams                                         | 13,000 beams                                     | Bitmap input format and resampling              |

|                      | Beam<br>blanker       | 110 x 10 MHz                                      | 13,000 x 49 x 70 MHz                             | Ge photodiode in 65 nm<br>CMOS                  |

| Electron<br>Optics   | Illumination optics   | 1.5 x 1.5 mm <sup>2</sup>                         | 26 x 26 mm <sup>2</sup>                          | Conventional electrostatic optics               |

|                      | Projection<br>optics  | 25 nm spots over 1.5 x 1.5 mm <sup>2</sup>        | 25 nm spots over 26 x<br>26 mm <sup>2</sup>      | Yield optimization and mechanical stabilization |

|                      | Contamination         | 40 ppm dose change per<br>wafer (PMMA)            | Same + plasma<br>cleaning every ~ 1000<br>wafers | Plasma cleaning                                 |

| Wafer<br>positioning | Thermal<br>stability  | 1 s                                               | 360 s, 1 wafer exposure                          | MAPPER proprietary                              |

|                      | Position<br>stability | 50 nm                                             | 1 nm                                             | Interferometer control<br>and EMC reductions    |

| Infrastructure       | Process<br>(resist)   | 40 nm in PMMA (60 uC/cm2)<br>and HSQ (100 uc/cm2) | 30 nm in 'industrial resist' @ 30 uC/cm2         | Test available resists for EUV                  |

|                      | Data<br>preparation   | Proximity correction verified by simulation       | Proximity correction verified in resist          | Leti + TSMC tools to verify assumptions         |

#### Conclusions

- MAPPER's technology provides a 10 wph system on a 1 m<sup>2</sup> footprint at low cost

- MAPPER's technology is an alternative for both direct patterning and pitch splitting with cutting and filling, this makes the technology viable for > 10 critical layers / chip

- MAPPER has installed two machines in the field, one at TSMC and one at CEA Leti

- Both machines, designed for 45 nm hp resolution, resolve ~ 30 nm hp in CAR

- At CEA-Leti a tool assessment and infrastructure program is ongoing: IMAGINE

- Solutions for scaling to 10 wph are available and are scalable for at least 3 generations

- In our opinion there are no fundamental roadblocks left

Thank you